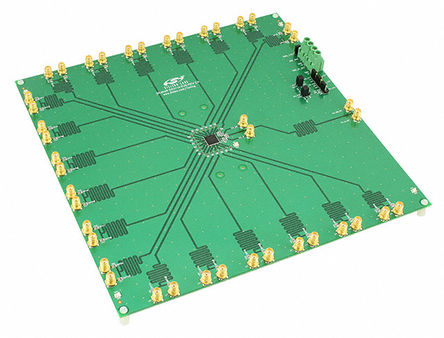

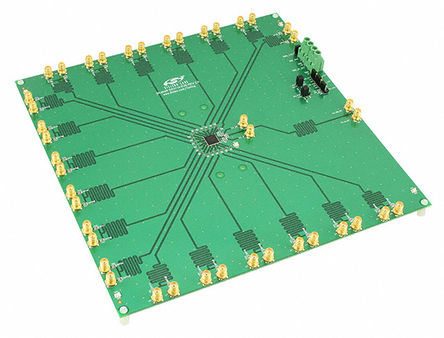

Silicon Laboratories �� Si53112-EK �� PCIe ʱ�ӺͿ����������ṩÿ���ظ����ܣ����ڷ��� PCI Express? Gen1/2/3 �������ʱ��Ӧ�á� ��Щʱ���������ͻ��������ʵ������������ܹ��ṩ�ߴ� 50% ������������ PCI-Express ������� Silicon Labs Si53112-EK PCIe ʱ���������ͻ�������ȫ���ɶ˽ӵ����������� BOM �ɱ�����ռ�Ҫ�����Ƹ����ԡ�

Si53112 �ǵ��ʡ�12 ������ʱ�ӻ����������� Intel DB1200ZL ������������Ҫ��

ʮ���� 0.7 V ���ʡ�����ʽ HCSL ���� PCIe Gen 3 ���

���� OE HW ���ţ�����ÿ�����ʱ��

100 MHz /133 MHz PLL ������֧�� PCIe �� QPI

PLL ���� SW SMBUS ��̸��� HW ���ŵı���ֵ

9 �� SMBUS ��ַ

���� SMBus ��ַ�����ڵ��������� 3.3 V ��Դ��ѹ�������������������

PLL ����·ģʽ

����չƵ

1.05 �� 3.3 V ����/�����Դ��ѹ

50 ps ��������ƫб

50 ps cyc-cyc ������PLL ģʽ��

������������� Intel? QPI��PCIe Gen 1/Gen 2/Gen 3��

100 ps ���뵽�����ʱ

�㷺���¶ȷ�Χ���C40 �� 85 ��C

��װ��64 ���� QFN

|

|